- 您现在的位置:买卖IC网 > Sheet目录1203 > COREFFT-RM (Microsemi SoC)IP MODULE COREFFT

�� �

�

�

�CoreFFT� Fast� Fourier� Transform�

�Buffering� Scheme�

�The� CoreFFT� module� has� one� radix-2� butterfly,� two� input�

�memory� banks� implementing� a� ping-pong� input� buffer,�

�and� one� output� buffer� (� Figure� 2� on� page� 4� ).�

�Both� of� the� identical� memory� banks� can� store� N� complex�

�samples.� Each� bank� consists� of� two� memory� blocks,� each�

�of� N� /� 2� complex� words,� so� it� can� read/write� two� complex�

�samples� per� clock.� Thus,� the� memory� bandwidth� is�

�tree.� The� switch� output� samples� are� then� routed� to� the�

�butterfly� P� and� Q� inputs.� Table� 3� shows� a� 16-point� FFT�

�example� of� how� Read� Switch� rearranges� sample� indices�

�coming� from� the� Mem� 0� and� Mem� 1� of� the� input�

�memory� bank.�

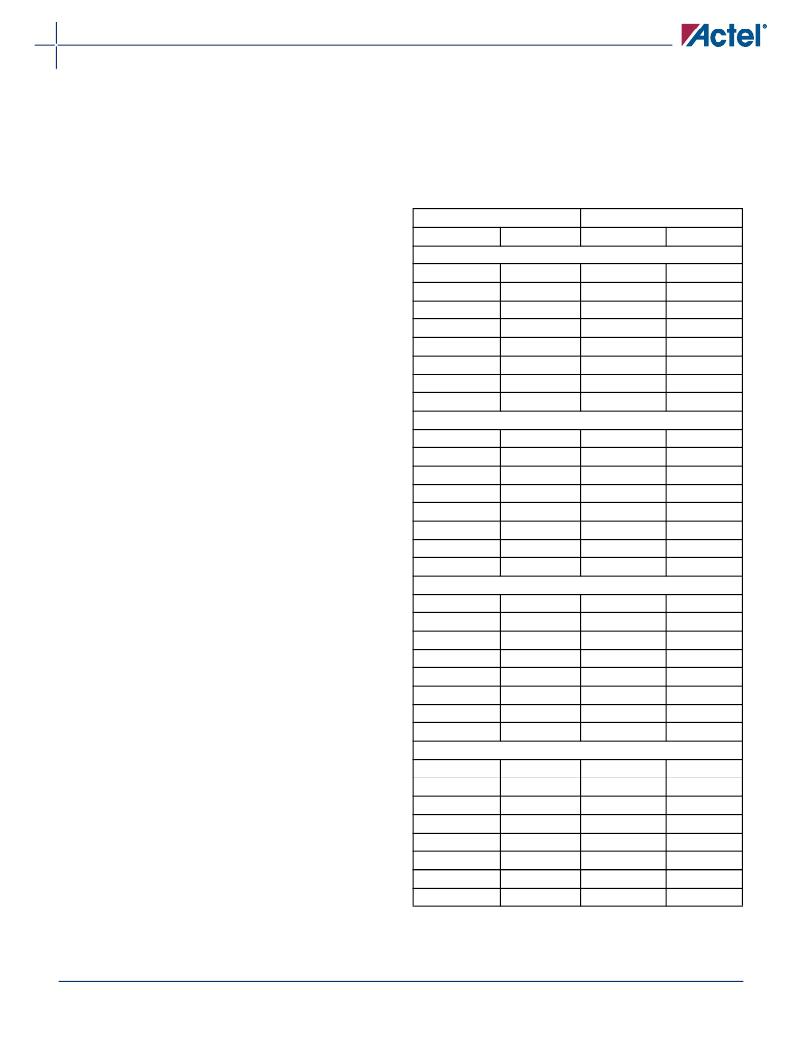

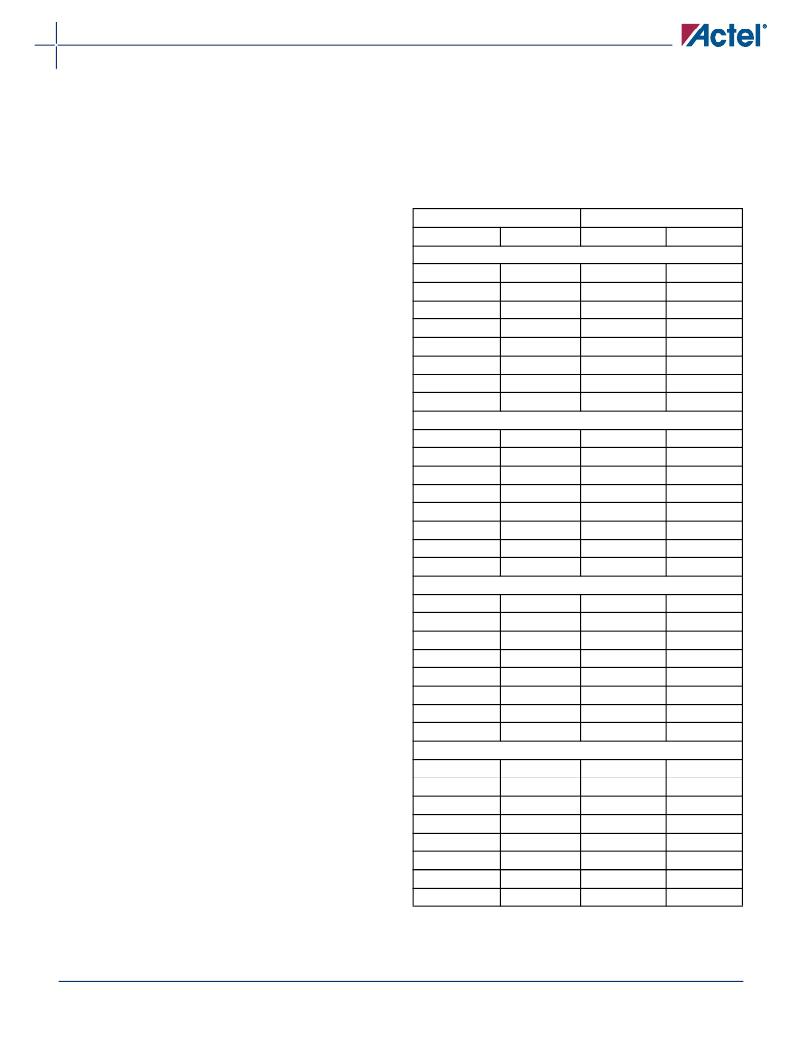

�Table� 3� ?� Sample� Indices� before� and� after� Read� Switch� for�

�16-Point� FFT� Example�

�Input� From� Output�

�(4� � b� )� bits� per� clock� cycle.� Internal� logic� controls� the�

�Mem� 0�

�Mem� 1�

�P�

�Q�

�ping-pong� switching� between� the� banks� so� a� data-source�

�Stage� 1�

�host� only� sees� the� buffer� ready� to� accept� new� data.� The�

�buffer� not� accepting� data� is� used� by� the� in-place� FFT�

�engine� as� working� memory.�

�This� ping-pong� buffering� architecture� increases� the�

�efficiency� of� the� FFT� engine.� While� one� of� the� two�

�identical� ping-pong� input� banks� is� involved� in� current� FFT�

�computation,� the� other� is� available� for� the� downloading�

�of� the� next� frame� of� input� data.� As� a� result,� the� FFT�

�engine� does� not� sit� idle� waiting� for� fresh� data� to� fill� the�

�input� buffer.� From� the� data-source� host� standpoint,� the�

�14�

�6�

�12�

�4�

�10�

�2�

�8�

�0�

�15�

�7�

�13�

�5�

�11�

�3�

�9�

�1�

�7�

�6�

�5�

�4�

�3�

�2�

�1�

�0�

�15�

�14�

�13�

�12�

�11�

�10�

�9�

�8�

�core� is� capable� of� receiving� a� data� burst� anywhere� within�

�Stage� 2�

�the� FFT� computational� period.� When� the� module� has�

�finished� processing� the� current� data� frame� and� the� input�

�buffer� bank� has� been� filled� with� another� data� frame,� the�

�memory� ping-pong� banks� are� swapped,� and� the� data�

�load� and� computation� continues� on� the� alternate�

�memory� banks.�

�The� last� stage� of� the� FFT� computation� uses� an� out-of-�

�place� scheme—the� FFT� final� results� are� routed� to� the�

�14�

�10�

�12�

�8�

�6�

�2�

�4�

�15�

�11�

�13�

�9�

�7�

�3�

�5�

�11�

�10�

�9�

�8�

�3�

�2�

�1�

�15�

�14�

�13�

�12�

�7�

�6�

�5�

�output� data� buffer.� The� results� appear� at� the� FFT� engine�

�output� in� bit-reversed� order.� A� bit-reversed� write� address�

�is� used� when� writing� the� results� to� the� output� buffer� to�

�restore� the� data� to� normal� read� address� order.� The� last�

�stage� results� remain� valid� until� the� FFT� engine� is� ready� to�

�store� the� results� of� the� next� data� frame.�

�The� CoreFFT� generator� also� calculates� the� twiddle� factors�

�required� by� the� FFT� algorithm.� At� power-up,� the� twiddle�

�factors� generated� are� written� to� the� twiddle� factor�

�lookup� table� (Twiddle� LUT).�

�FFT� Computation�

�An� FFT� computational� cycle� starts� when� input� data� is�

�stored� in� the� active� ping-pong� buffer� bank� and� the� FFT�

�engine� has� finished� processing� the� previous� N� data�

�samples.� Each� memory� bank� comprises� two� bb� -bit-wide�

�memories� (Mem� 0� and� Mem� 1),� supplying� a� data�

�bandwidth� of� (4� � b� )� bits� per� clock� cycle� (two� complex�

�samples� per� clock� cycle).� Even� input� samples� D� i� (i� =� 0,� 2,� 4,� …,�

�N� –� )� are� stored� in� Mem� 0,� odd� samples� in� Mem� 1.�

�The� Read� Switch� function� is� used� to� rearrange� the� two�

�0�

�14�

�12�

�10�

�8�

�6�

�4�

�2�

�0�

�14�

�12�

�10�

�8�

�6�

�4�

�2�

�0�

�1�

�15�

�13�

�11�

�9�

�7�

�5�

�3�

�1�

�15�

�13�

�11�

�9�

�7�

�5�

�3�

�1�

�Stage� 3�

�Stage� 4�

�0�

�13�

�12�

�9�

�8�

�5�

�4�

�1�

�0�

�14�

�12�

�10�

�8�

�6�

�4�

�2�

�0�

�4�

�15�

�14�

�11�

�10�

�7�

�6�

�3�

�2�

�15�

�13�

�11�

�9�

�7�

�5�

�3�

�1�

�sample� pairs� read� from� the� input� bank� to� match� the�

�input� sample� order� required� by� the� DIT� FFT� algorithm�

�v4.0�

�5�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

COREFIR-RM

IP MODULE COREFIR

COREPCIF-RM

IP MODULE COREPCIF

COREU1LL-AR

IP MODULE COREU1LL

COREU1PHY-AR

IP MODULE COREU1PHY

CORR-8BIT-XM-UT2

SITE LICENSE IP CORRELATOR XP

CP2-GSA-L

CONN SHIELD LOWER TYPE A 22

CP2-HSA110-1

CONN SHROUD CPCI 2MM TYPE A 22

CP2-HSC055-4

CONN SHROUD CPCI 2MM TYPE C 11

相关代理商/技术参数

COREFFT-RMFL

功能描述:IP MODULE 制造商:microsemi corporation 系列:- 零件状态:在售 类型:许可证 应用:- 版本:- 许可长度:- 许可 - 用户明细:- 操作系统:- 配套使用产品/相关产品:Microsemi 器件 媒体分发类型:- 标准包装:1

COREFFT-UR

功能描述:HW/SW/OTHER 制造商:microsemi corporation 系列:* 零件状态:在售 标准包装:1

COREFIR-AR

制造商:ACTEL 制造商全称:Actel Corporation 功能描述:CoreFIR Finite Impulse Response (FIR) Filter Generator

COREFIR-EV

制造商:ACTEL 制造商全称:Actel Corporation 功能描述:CoreFIR Finite Impulse Response (FIR) Filter Generator

COREFIR-RM

功能描述:IP MODULE COREFIR RoHS:否 类别:编程器,开发系统 >> 软件 系列:* 标准包装:1 系列:ISE® 设计套件 类型:订阅 适用于相关产品:Xilinx FPGAs 其它名称:Q4986209T1081384

COREFIR-UR

制造商:ACTEL 制造商全称:Actel Corporation 功能描述:CoreFIR Finite Impulse Response (FIR) Filter Generator

COREFIR-XX

制造商:ACTEL 制造商全称:Actel Corporation 功能描述:CoreFIR Finite Impulse Response (FIR) Filter Generator

COREMP7

制造商:ACTEL 制造商全称:Actel Corporation 功能描述:CoreMP7